## 3.3V, PCI Express® 3.0 2-Lane, 2:1 Mux/DeMux Switch

#### **Features**

→ 4 Differential Channel, 2:1 Mux/DeMux

→ PCI Express<sup>®</sup> 3.0 Performance, 8.0Gbps

→ Pinout optimized for placement between two PCIe slots

→ Bi-directional operation

→ Low Bit-to-Bit Skew, 10ps max

→ Low Crosstalk: -48dB @4GHz

→ High Off Isolation: -22dB @4GHz

→ Low Insertion Loss: -1.6dB @4GHz

→ Return Loss: -15dB @4GHz

→ V<sub>DD</sub> Operating Range: +3.3V

→ ESD Tolerance: 2kV HBM

→ Low channel-to-channel skew, 20ps max

→ Packaging (Pb-free & Green):

42-contact, TQFN (ZH42)

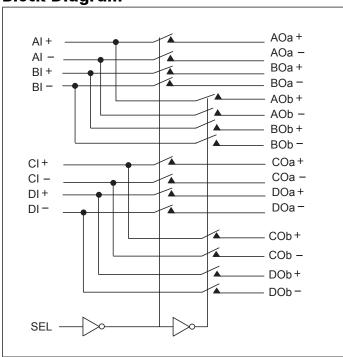

## **Block Diagram**

#### **Truth Table**

| Function    | SEL |  |  |  |  |

|-------------|-----|--|--|--|--|

| xIy to xOay | L   |  |  |  |  |

| xIy to xOby | Н   |  |  |  |  |

### **Description**

Pericom Semiconductor's PI3PCIE3415 is an 8 to 4 differential channel multiplexer/demultiplexer switch. This solution can switch 2 full PCI Express® 3.0, lanes to one of two locations. Using a unique design technique, Pericom has been able to minimize the impedance of the switch such that the attenuation observed through the switch is negligible. The unique design technique also offers a layout targeted for PCI Express signals, which minimizes the channel to channel skew as well as channel to channel crosstalk as required by the PCI Express specification.

### **Application**

Routing of PCI Express 3.0, DP1.2, USB3.0, SAS2.0, SATA3.0, XAUI, RXAUI signals with low signal attenuation.

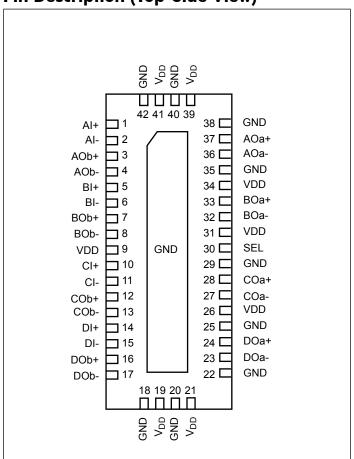

### Pin Description (Top-Side View)

## **Signal Descriptions**

| Pin Number                         | Pin Name   | Туре                                         | Description                                                                                                                                                                      |

|------------------------------------|------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2                               | AI+, AI-   | Differential I/O                             | Differential I/O pair from PCIE signal source. Signal is routed to the AOa+, AOa- pin respectively when SEL=0. Signal is routed to the AOb+, AOb- pin respectively when SEL = 1. |

| 37, 36                             | AOa+, AOa- | Differential I/O                             | Differential analog pass-through I/O. Signal from AI+ and AI-is routed to AOa+ and AOa- respectively when SEL=0.                                                                 |

| 3, 4                               | AOb+, AOb- | Differential I/O                             | Differential analog pass-through I/O. Signal from AI+ and AI- is routed to AOb+ and AOb- respectively when SEL=1.                                                                |

| 5, 6                               | BI+, BI-   | Differential I/O                             | Differential I/O pair from PCIE signal source. Signal is routed to the BOa+, BOa- pin respectively when SEL=0. Signal is routed to the BOb+, BOb- pin respectively when SEL = 1. |

| 33, 32                             | BOa+, BOa- | Differential I/O                             | Differential analog pass-through I/O. Signal from BI+ and BI- is routed to BOa+ and BOa- respectively when SEL=0.                                                                |

| 7, 8                               | BOb+, BOb- | Differential I/O                             | Differential analog pass-through I/O. Signal from BI+ and BI- is routed to BOb+ and BOb- respectively when SEL=1.                                                                |

| 10, 11                             | CI+, CI-   | Differential I/O                             | Differential I/O pair from PCIE signal source. Signal is routed to the COa+, COa- pin respectively When SEL=0. Signal is routed to the COb+, COb- pin respectively when SEL = 1. |

| 28, 27                             | COa+, COa- | Differential I/O                             | Differential analog pass-through I/O. Signal from CI+ and CI- is routed to COa+, COa- pin respectively when SEL = 0.                                                             |

| 12, 13                             | COb+, COb- | Differential I/O                             | Differential analog pass-through I/O. Signal from CI+ and CI- is routed to COb+, COb- pin respectively when SEL = 1.                                                             |

| 14, 15                             | DI+, DI-   | Differential I/O                             | Differential I/O pair from PCIE signal source. Signal is routed to the DOa+, DOa- pin respectively When SEL=0. Signal is routed to the DOb+, DOb- pin respectively when SEL = 1. |

| 24, 23                             | DOa+, DOa- | Differential I/O                             | Differential analog pass-through I/O. Signal from DI+ and DI-<br>is routed to DOa+, DOa- pin respectively when SEL = 0.                                                          |

| 16, 17                             | DOb+, DOb- | Differential I/O                             | Differential analog pass-through I/O. Signal from DI+ and DI-<br>is routed to DOb+, DOb- pin respectively when SEL = 1.                                                          |

| 18, 20, 22, 25, 29, 35, 38, 40, 42 | GND        | Ground input                                 | Ground                                                                                                                                                                           |

| 30                                 | SEL        | 3.6V tolerant low-voltage single-ended input | SEL controls the mux through a flow-through latch.                                                                                                                               |

| 9, 19, 21, 26, 31,<br>34, 39, 41   | VDD        | Power supply                                 | Power, 3.3V ±10%                                                                                                                                                                 |

### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | 65°C to +150°C |

|------------------------------------|----------------|

| Supply Voltage to Ground Potential | 0.5V to +4.6V  |

| Channel DC Input Voltage           | 0.5V to 1.5V   |

| DC Output Current                  | 120mA          |

| Power Dissipation                  | 0.5W           |

| SEL DC Input Voltage               | 0.5V to 4.6V   |

Note: Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Electrical Characteristics** Recommended Operating Conditions

| Symbol            | Parameter                                         | Conditions                  | Min | Тур  | Max | Units   |

|-------------------|---------------------------------------------------|-----------------------------|-----|------|-----|---------|

| $V_{\mathrm{DD}}$ | 3.3V Power Supply                                 |                             | 3.0 | 3.3  | 3.6 | V       |

| $I_{\mathrm{DD}}$ | Total current from V <sub>DD</sub> 3.3V supply    | SEL = 0V or V <sub>DD</sub> | 0   | 0.15 | 1   | mA      |

| T <sub>CASE</sub> | Case temperature range for operation within spec. |                             | -40 |      | 85  | Celsius |

## DC Electrical Characteristics $(T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, V_{DD} = 3.3\text{V} \pm 10\%)$

| Parameter           | Description                         | <b>Test Conditions</b>                             | Min | Typ <sup>(1)</sup> | Max | Units |

|---------------------|-------------------------------------|----------------------------------------------------|-----|--------------------|-----|-------|

| V <sub>IH-SEL</sub> | Input high level, SEL input         |                                                    | 2.0 |                    | 3.6 | V     |

| $V_{\text{IL-SEL}}$ | Input Low Level, SEL input          |                                                    | 0   |                    | 0.8 | V     |

| I <sub>IN_SEL</sub> | Input Leakage Current,<br>SEL input | Measured with input at VIH-SEL max and VIL-SEL min | -10 |                    | 10  | uA    |

| $I_{IH}$            | Input High Current,<br>xI, xO       | $V_{DD} = Max, V_{IN} = 1.5V$                      | -10 |                    | 10  | uA    |

| $I_{IL}$            | Input Low Current,<br>xI, xO        | $V_{DD} = Max, V_{IN} = 0V$                        | -10 |                    | 10  | uA    |

| $I_{IH}$            | Input High Current,<br>SEL          | $V_{DD} = Max, V_{IN} = V_{DD}$                    | -5  |                    | 5   | uA    |

| $I_{\mathrm{IL}}$   | Input Low Current,<br>SEL           | $V_{DD} = Max, V_{IN} = 0V$                        | -5  |                    | 5   | uA    |

| I <sub>OZH</sub>    | HighZ High Current<br>xOa, xOb      | $V_{DD} = Max, V_{IN} = 1.5V$                      | -10 |                    | 10  | uA    |

| I <sub>OZL</sub>    | HighZ Low Current<br>xOa, xOb       | $V_{DD} = Max, V_{IN} = 0V$                        | -10 |                    | 10  | uA    |

3

#### Note:

1. Typical values are at  $V_{DD} = 3.3V$ ,  $T_A = 25$ °C ambient and maximum loading.

## Dynamic Electrical Characteristics for xI+/-, xOy+/-

| Parameter           | Description                 | <b>Test Conditions</b> | Min.  | Typ.(1) | Max. | Units |

|---------------------|-----------------------------|------------------------|-------|---------|------|-------|

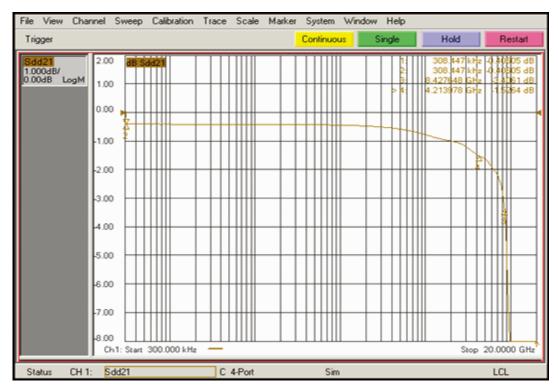

| DDU                 |                             | f=50MHz -1.25GHz       |       | -0.8    | -1.0 |       |

|                     | Differential Insertion Loss | f=1.25GHz - 2.5GHz     |       | -1.1    | -1.3 |       |

| DDIL                | Differential Insertion Loss | f=2.5GHz - 4GHz        |       | -1.6    | -1.9 |       |

|                     |                             | f=5.0GHz               |       | -1.7    | -2.0 |       |

|                     |                             |                        | -25.8 | -32.2   |      |       |

| DDII                | Differential Off Isolation  | f= 0 to 4.0GHz         | -20.6 | -25.8   |      |       |

| DDIL <sub>OFF</sub> | Differential Off Isolation  | 1= 0 to 4.0GHZ         | -17.6 | -22.0   |      |       |

|                     |                             |                        | -15.4 | -19.3   |      | 10    |

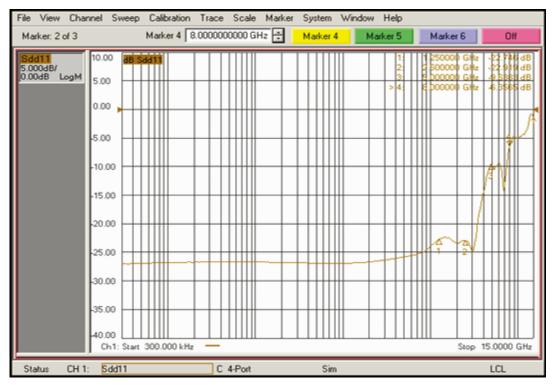

|                     |                             | f=50MHz - 1.25GHz      | -18.2 | -22.7   |      | dB    |

| DDDI                | D'G ('ID ( I                | f=1.25GHz - 2.5GHz     | -16.8 | -21.0   |      |       |

| DDRL                | Differential Return Loss    | f=2.5GHz - 4GHz        | -12   | -15.0   |      |       |

|                     |                             | f=5.0GHz               | -8    | -10.0   |      |       |

|                     |                             | f=50MHz -1.25GHz       | -44.8 | -56     |      |       |

| DDNEXT              | N F 10 (1)                  | f=1.25GHz - 2.5GHz     | -41.6 | -52     |      |       |

|                     | Near End Crosstalk          | f=2.5GHz - 4GHz        | -38.4 | -48     |      |       |

|                     |                             | f=5.0GHz               | -36   | -45     |      |       |

| BW                  | Bandwidth -3dB              |                        |       | 8.7     |      | GHz   |

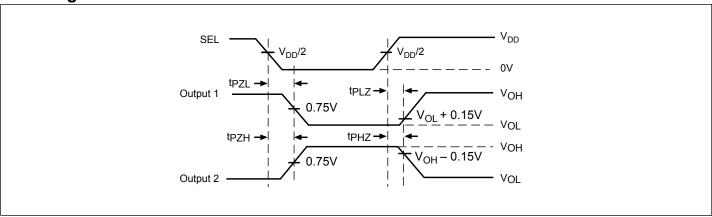

# **Switching Characteristics**

| Parameter                   | Description                                                 | <b>Test Conditions</b>      | Min.     | Тур. | Max. | Units |

|-----------------------------|-------------------------------------------------------------|-----------------------------|----------|------|------|-------|

|                             |                                                             | See "Test Circuit for       | 0.5      | 1.5  | 25   | ns    |

| $t_{PZH}, t_{PZL}$          | Line Enable Time - SEL to xI+/-, xOy+/-                     | Electrical Characteristics" | 0.5   15 |      |      |       |

| 1: D: 11 T: 0TI . 1 . 0 . / |                                                             | See "Test Circuit for       |          | _    | 25   |       |

| tPHZ, tPLZ                  | $t_{PHZ}, t_{PLZ}$ Line Disable Time - SEL to xI+/-, xOy+/- | Electrical Characteristics" | 0.5      | 5    | 25   | ns    |

| 4                           | Bit-to-bit skew within the same differential                | See "Test Circuit for       | 4        | 4    | 10   |       |

| t <sub>b-b</sub>            | pair                                                        | Electrical Characteristics" |          | 4    | 10   | ps    |

| t <sub>ch-ch</sub>          | Channel-to-channel skew                                     | See "Test Circuit for       |          |      | 20   |       |

|                             |                                                             | Electrical Characteristics" |          |      |      | ps    |

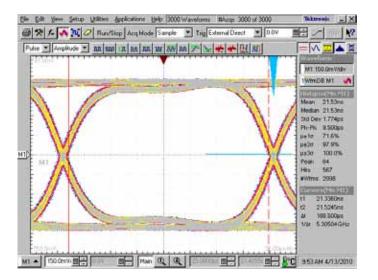

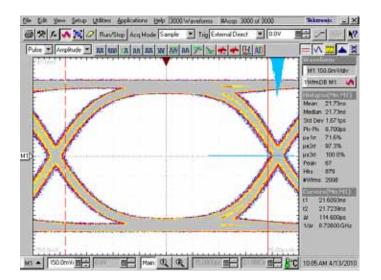

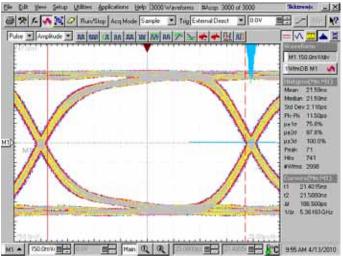

5.0 Gbps RX signal eye without PI3PCIE3415

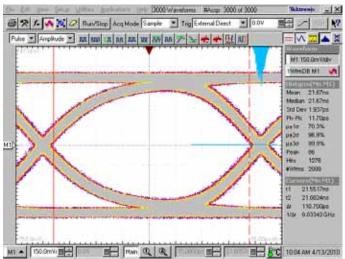

8.0 Gbps RX signal eye without PI3PCIE3415

5.0 Gbps RX signal eye with PI3PCIE3415

8.0 Gbps RX signal eye with PI3PCIE3415

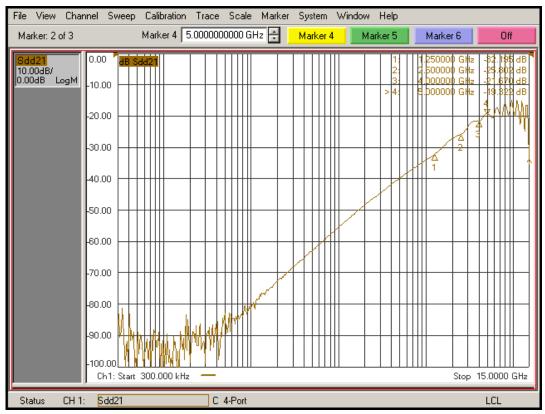

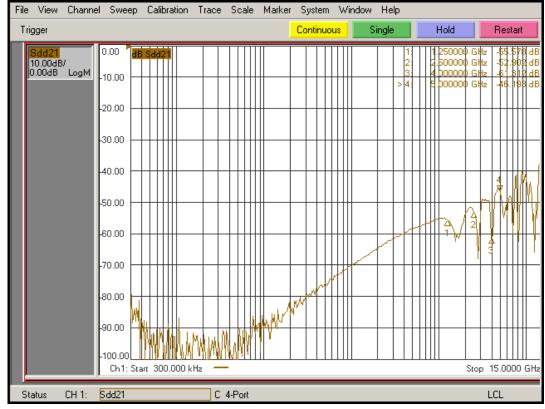

**Differential Insertion Loss**

**Differential Return Loss**

### **Differential Off Isolation**

#### **Differential Crosstalk**

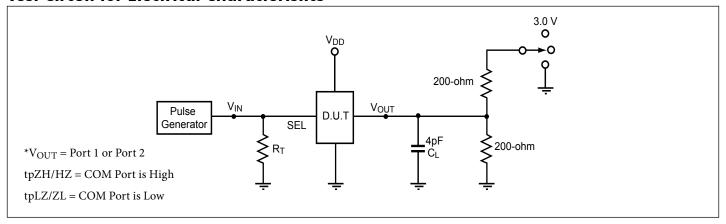

# Test Circuit for Electrical Characteristics $^{(1-5)}$

#### Notes:

- C<sub>L</sub> = Load capacitance: includes jig and probe capacitance. 1.

- 2. R<sub>T</sub> = Termination resistance: should be equal to Z<sub>OUT</sub> of the Pulse Generator

- 3. Output 1 is for an output with internal conditions such that the output is low except when disabled by the output control. output 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- 4. All input impulses are supplied by generators having the following characteristics:  $PRR \leq MHz, Z_O = 50\Omega, t_R \leq 2.5ns, t_F \leq 2.5ns.$

- 5. The outputs are measured one at a time with one transition per measurement.

#### **Switch Positions**

| Test                                 | Switch |

|--------------------------------------|--------|

| $t_{\mathrm{PLZ}}, t_{\mathrm{PZL}}$ | 3.0V   |

| $t_{\mathrm{PHZ}}, t_{\mathrm{PZH}}$ | GND    |

### **Switching Waveforms**

**Voltage Waveforms Enable and Disable Times**

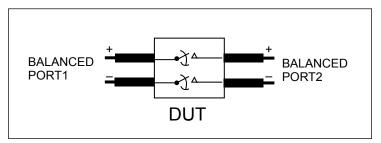

**Differential Insertion Loss and Return Test Circuit**

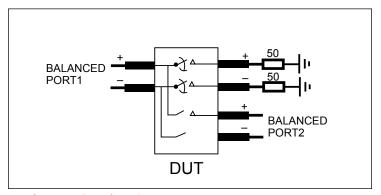

**Differential Off Isolation Test Circuit**

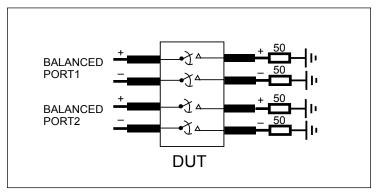

Differential Near End Xtalk Test Circuit

#### Note:

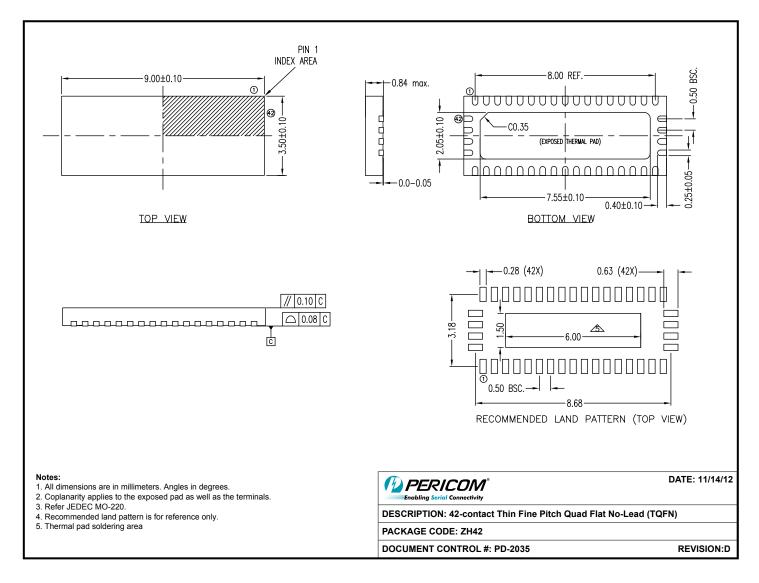

For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

# **Ordering Information**

| Ordering Code  | Package Code | Package Description              |

|----------------|--------------|----------------------------------|

| PI3PCIE3415ZHE | ZH           | Pb-free & Green, 42-contact TQFN |

10

#### Notes:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- "E" denotes Pb-free and Green

- Adding an "X" at the end of the ordering code denotes tape and reel packaging